Implementation

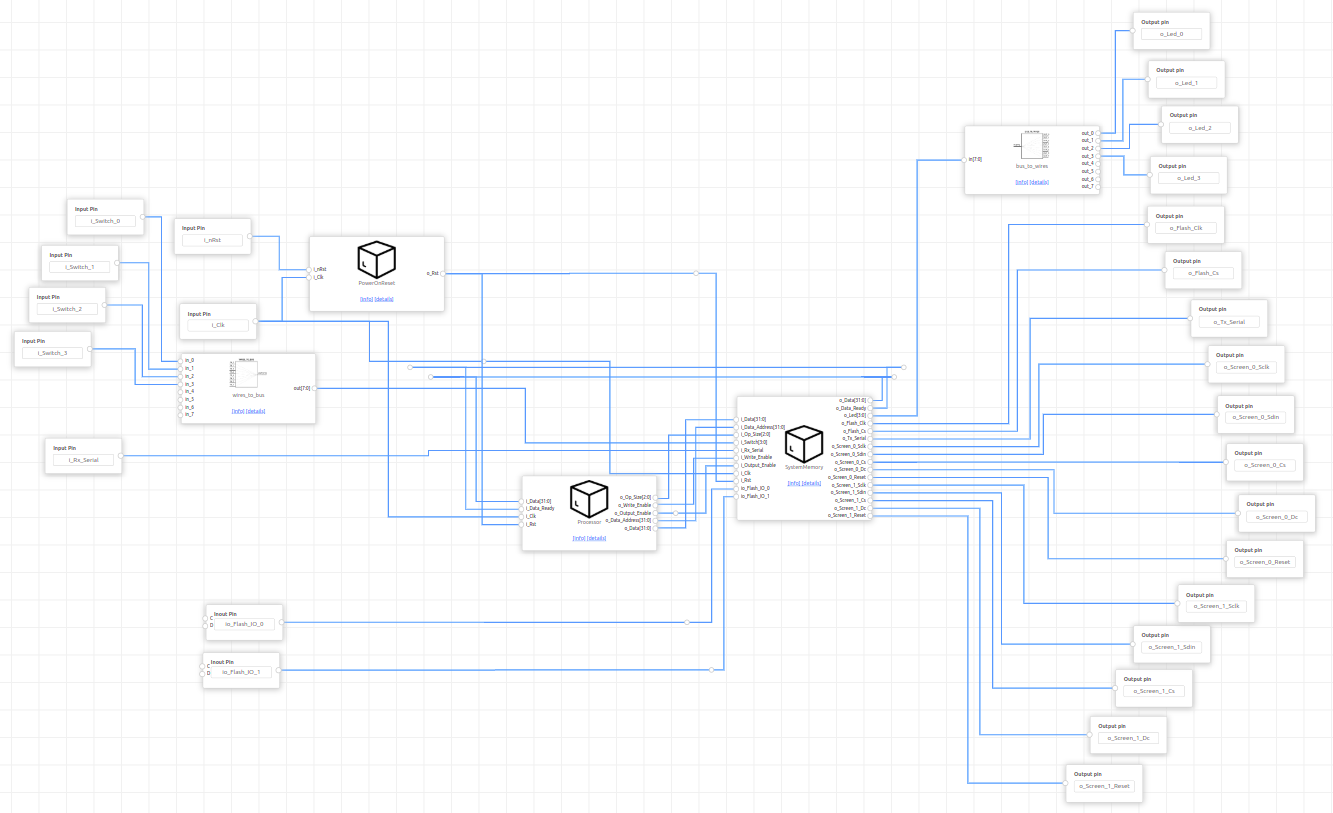

The design was made in Verilog, primarily targeting the von Braun Labs’ DevChipBoard, containing the Tang Nano 9k board, running at a base frequency of 27MHz. The RISC-V core is composed of a simple datapath and a multicycle control unit (with up to 4 states).

The core implements the RV32I unprivileged base ISA, enabling the execution of most of the software. The board Flash memory is read in Dual SPI by the controller in enhanced mode, meaning the command doesn’t need to be sent at every read, taking roughly 2.5us to read an instruction or (constant) data.

The microcontroller implements a simple memory mapping system, enabling an easy inclusion of peripherals. Four basic peripherals are implemented: Led & Switch, UART, and two OLED displays controllers, all accessible via code in a memory address.

No Comments